## Multiplexer con chip select

Alcuni di voi, ieri, mi hanno fatto vedere un esercizio che potrebbe capitare all'esame ma che forse non ho spiegato nel modo in cui lo intendeva il professore. Quindi ho pensato fosse una buona idea fornirvi anche la soluzione che probabilmente lui preferisce all'esame.

Il problema lo abbiamo già affrontato: implementare una funzione logica in 4 variabili con soli multiplexer a 3 bit di controllo (e 8 input, conseguentemente: 8 = 2³). La soluzione proposta è leggermente diversa: invece di collegare la quarta variabile ad alcuni degli input di un unico multiplexer, si crea un circuito con 2 multiplexer, tra i quali possiamo scegliere tramite la quarta variabile. Vi faccio prima un esempio semplice, poi lo applichiamo all'esercizio n° 3 della esercitazione 5 (EX5.pdf nella cartella Google Drive).

Vorremmo, ad esempio, valutare la semplice espressione logica ABC+ $\overline{A}$   $\overline{B}$   $\overline{C}$  + E tramite multiplexer.

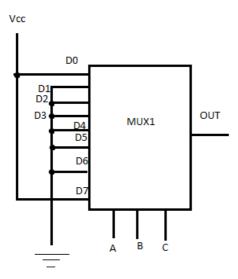

Risolviamo, in primo luogo, l'espressione logica con solo 3 variabili: A, B e C, nel caso che stiamo esaminando. Come è facile vedere, dobbiamo dare il segnale alto solo agli input  $D_0$  e  $D_7$ , generando così il mux (chiameremo in questo modo i multiplexer, d'ora in poi) in figura.

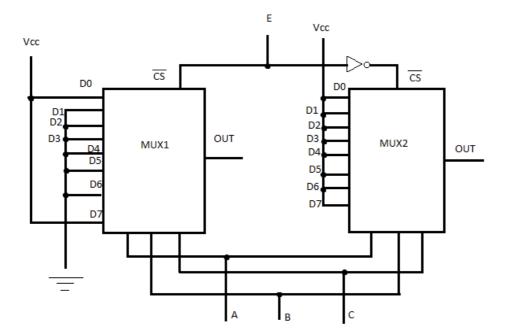

Ora, però, vogliamo fare in modo che il nostro circuito riconosca anche l'espressione generata dalla sola variabile logica E. Come fare? L'idea che vi sottopongo è la seguente: fornire il circuito mux di un bit di chip selection (che chiameremo  $\overline{CS}$ ) che ci permetta di selezionarlo o meno. Collegheremo, poi, questo bit alla variabile logica E. Quindi, il primo mux (quello disegnato sopra) dovrà attivarsi quando E è 0, mentre creeremo un secondo mux che restituirà 1 a vuoto che, invece, sarà selezionato nel caso in cui E sia 1. Vi ricordo che un circuito viene selezionato (o usato, se preferite) nel momento in cui il valore che arriva alla porta  $\overline{CS}$  è 0. Se le parole non sono state abbastanza chiare, guardate la figura, che potrebbe chiarificarvi la situazione.

Il circuito mostrato in questa seconda figura implementa esattamente quanto detto finora:

- Se E ha valore 0, la porta  $\overline{CS}$  del mux<sub>1</sub> riceve un segnale basso (0), attivando proprio il mux<sub>1</sub>. Da esso viene calcolato il valore della funzione logica, escludendo la variabile E. Questo valore viene mandato in output. Allo stesso tempo, il mux<sub>2</sub> non viene selezionato, (la sua porta logica  $\overline{CS}$  riceve un segnale alto) e quindi non fa nulla.

- Se E ha valore 1, la porta  $\overline{CS}$  del mux<sub>2</sub> riceve un segnale basso (0), che dunque viene attivato. Visto che è un circuito che restituisce sempre 1, farà uscire dal proprio output il valore 1, a prescindere dai valori presenti sui bit di controllo. Contemporaneamente mux<sub>1</sub> non viene selezionato, e quindi non farà nulla.

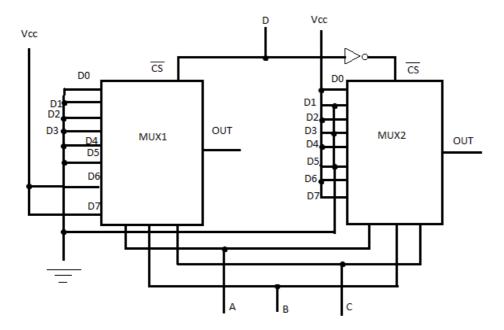

Per quanto riguarda l'esercizio 3 dell'esercitazione 5, invece, la situazione è leggermente differente, a causa della forma della funzione logica in analisi. La funzione era: AB+ $\overline{C}D$ . Attenzione: non confondete la variabile logica D con le porte dei valori d'ingresso dei mux  $D_k$ . Sarà, dunque, D la nostra variabile che attiverà o meno le porte  $\overline{CS}$  dei due mux che stiamo per disegnare. Il mux selezionato da D=0 dovrà, quindi, realizzare solo la funzione logica AB, mentre quello selezionato da D=1 dovrà realizzare la funzione logica AB+ $\overline{C}$ .

Per rendere più chiara la figura, ve la racconto prima a parole:

- Nel  $mux_1$ :

- le porte D<sub>6</sub> e D<sub>7</sub> sono collegate alla massa (attivano gli AND del tipo 11x)

- o tutte le altre porte sono collegate a terra

- Nel mux<sub>2</sub>:

- $\circ$  le porte  $D_0$ ,  $D_2$ ,  $D_4$ ,  $D_6$  sono collegate alla massa (implementano  $\overline{C}$ , attivando tutti gli AND del tipo xx0)

- o la porta D<sub>7</sub> è collegata alla massa, poiché implenta AB (attiva l'unico ingresso non ancora attivato del tipo 110, cioè 111)

- le altre porte sono collegate a terra.

La variabile logica D ha esattamente lo stesso ruolo della variabie logica E dell'esempio visto in precedenza. A seguito la figura del nuovo circuito.

Se qualcosa ancora non fosse chiaro, non esitate a chiedere, sia pubblicamente che in PM. Se molti di voi dovessero ancora avere qualche problema su questa soluzione, possiamo tranquillamente metterci d'accordo e vederci prima dell'esame per discuterne a voce.